Flynnsche Klassifikation

| Single Instruction |

Multiple Instruction | |

|---|---|---|

| Single Data |

SISD | MISD |

| Multiple Data |

SIMD | MIMD |

Die flynnsche Klassifikation[1][2] (auch Flynn’sche Taxonomie genannt) ist eine Unterteilung von Rechnerarchitekturen, welche 1966 von Michael J. Flynn publiziert wurde.[3] Dabei werden die Architekturen nach der Anzahl der vorhandenen Befehls- (instruction streams) und Datenströme (data streams) unterteilt. Die verwendeten vierbuchstabigen Abkürzungen SISD, SIMD, MISD und MIMD wurden aus den Anfangsbuchstaben der englischen Beschreibungen abgeleitet, zum Beispiel steht SISD für „Single Instruction, Single Data“.

SISD (Single Instruction, Single Data)

[Bearbeiten | Quelltext bearbeiten]Unter SISD-Rechnern versteht man traditionelle Einkernprozessor-Rechner, die ihre Aufgaben sequentiell abarbeiten. SISD-Rechner sind z. B. Personal-Computer (PCs) oder Workstations, welche nach der Von-Neumann- oder der Harvard-Architektur aufgebaut sind. Bei ersterer wird für Befehle und Daten die gleiche Speicheranbindung verwendet, bei letzterer sind sie getrennt.

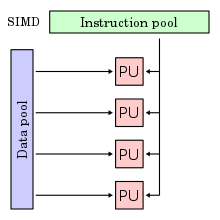

SIMD (Single Instruction, Multiple Data)

[Bearbeiten | Quelltext bearbeiten]

SIMD-Computer, auch bekannt als Array-Prozessoren oder Vektorprozessoren, dienen der schnellen Ausführung gleichartiger Rechenoperationen auf mehrere gleichzeitig eintreffende oder zur Verfügung stehende Eingangsdatenströme.

SIMD-fähige Prozessoren eignen sich beispielsweise gut für die Verarbeitung von Bild-, Ton- und Videodaten, weil in diesen Bereichen die zu verarbeitenden Daten meist hochgradig parallelisierbar sind; so sind z. B. bei einem Videoschnitt die Operationen für die vielen einzelnen Bildpunkte identisch. Theoretisch optimal wäre hier die Ausführung durch einen einzigen, auf alle Punkte anzuwendenden Befehl. Des Weiteren sind im Multimedia- und Kommunikationsbereich erforderliche Operationen häufig keine einfachen, einzelnen Operationen, sondern eher umfangreichere Befehlsketten. Das Einblenden eines Bildes vor einem Hintergrund ist beispielsweise ein komplexer Vorgang aus Maskenbildung mittels XOR, Vorbereitung des Hintergrundes mittels AND und NOT, sowie der Überlagerung der Teilbilder durch OR. Dieser Anforderung wird durch die Bereitstellung neuer komplexer Befehle entsprochen. So vereinigt z. B. der MMX-Befehl PANDN eine Invertierung und Und-Verknüpfung der Form x = y AND (NOT x).

Viele moderne Prozessorarchitekturen (wie PowerPC und x86) beinhalten inzwischen SIMD-Erweiterungen, das heißt spezielle zusätzliche Befehlssätze, die mit einem Befehlsaufruf gleichzeitig mehrere gleichartige Datensätze verarbeiten.

Allerdings muss man zwischen Befehlen unterscheiden, die lediglich gleichartige Rechenoperationen ausführen und anderen, die bis in den Bereich der DSP-Funktionalität hineinreichen (beispielsweise ist AltiVec in dieser Hinsicht wesentlich leistungsfähiger als 3DNow).

Bei heutigen Prozessoren sind Single Instruction Multiple Data-Einheiten Stand der Technik:

| Entwickler | Prozessorarchitektur | SIMD-Einheit |

|---|---|---|

| ARM Ltd. | ARM32 / ARM64 | NEON |

| IBM (AIM) | Power / PowerPC | AltiVec / VSX |

| Intel u. a. | x86 (x86-16 / IA-32 / x64) | 3DNow / SSE / AVX |

Siehe auch:

- MMX, SSE, 3DNow, AltiVec, SSE2, SSE3, SSSE3, SSE4, SSE5 und AVX.

- Feldrechner – mehrere Recheneinheiten berechnen parallel auf verschiedenen Daten die gleiche Operation

- Vektorprozessor – quasi-parallele Bearbeitung mehrerer Daten durch Pipelining

MISD (Multiple Instruction, Single Data)

[Bearbeiten | Quelltext bearbeiten]Eine Architektur von Großrechnern bzw. Supercomputern. Die Zuordnung von Systemen zu dieser Klasse ist schwierig, sie ist deshalb umstritten. Viele sind der Meinung, dass es solche Systeme eigentlich nicht geben dürfte. Man kann aber fehlertolerante Systeme, die redundante Berechnungen ausführen, in diese Klasse einordnen. Ein Beispiel für dieses Prozessorsystem ist ein Schachcomputer.

Eine Umsetzung ist das Makropipelining, bei dem mehrere Recheneinheiten hintereinander geschaltet sind. Eine weitere sind redundante Datenströme zur Fehlererkennung bzw. -korrektur.

MIMD (Multiple Instruction, Multiple Data)

[Bearbeiten | Quelltext bearbeiten]Eine Architektur von Großrechnern bzw. Supercomputern. MIMD-Computer führen gleichzeitig verschiedene Operationen auf verschieden gearteten Eingangsdatenströmen durch, wobei die Verteilung der Aufgaben an die zur Verfügung stehenden Ressourcen, meistens durch einen oder mehrere Prozessoren des Prozessorverbandes, selbst zur Laufzeit durchgeführt wird. Jeder Prozessor hat Zugriff auf die Daten anderer Prozessoren.

Man unterscheidet eng gekoppelte Systeme und lose gekoppelte Systeme. Eng gekoppelte Systeme sind Mehrprozessorsysteme, während lose gekoppelte Systeme Multicomputersysteme sind.

Multiprozessorsysteme teilen sich den vorhandenen Speicher und sind somit also ein Shared-Memory-System. Diese Shared-Memory-Systeme lassen sich weiter in UMA (uniform memory access), NUMA (non-uniform memory access) und COMA (cache-only memory access) unterteilen.

Man versucht bei MIMD eine Problemstellung durch die Lösung von Teilproblemen in den Griff zu bekommen. Dabei entsteht wiederum das Problem, dass verschiedene Teilstränge des Problems miteinander synchronisiert werden müssen.

Ein Beispiel in diesem Falle wäre das UNIX-Kommando make. Hier können auch mit mehreren Prozessoren mehrere zusammengehörige Programmcodes gleichzeitig in Maschinensprache übersetzt werden.

Siehe auch:

- Transputer

- Verteiltes System – autonome Prozessoren, die gleichzeitig verschiedene Befehle auf verschiedenen Daten bearbeiten

Siehe auch

[Bearbeiten | Quelltext bearbeiten]- MSIMD, eine Architektur, die sich zwischen den Klassen SIMD und MIMD bewegt

Einzelnachweise

[Bearbeiten | Quelltext bearbeiten]- ↑ M. Flynn: Some Computer Organizations and Their Effectiveness, IEEE Trans. Comput., Band C-21, S. 948–960, 1972.

- ↑ Ralph Duncan: A Survey of Parallel Computer Architectures, IEEE Computer. Februar 1990, S. 5–16.

- ↑ Sigrid Körbler: Parallel Computing – Systemarchitekturen und Methoden der Programmierung, Seite 12.